## WIRELESS-SENSOR NETWORKS

#### FIND A FIT IN THE UNLICENSED BAND

Page 46

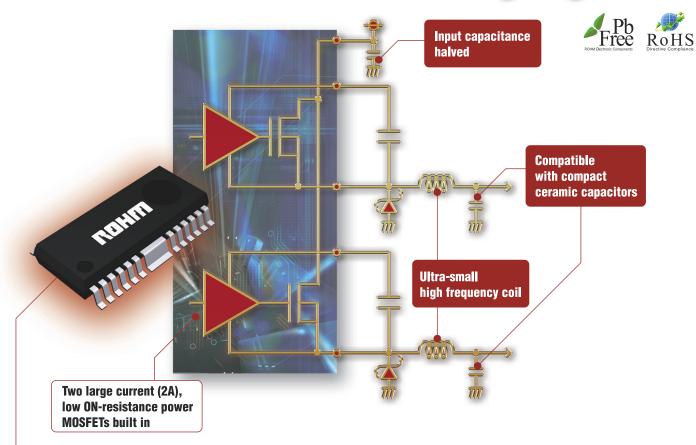

## High Frequency 25 M Power Designs ROHM Switching Regulators

#### **Dual-Output, High Frequency, Step-Down Switching Regulator**

BD9302FP

- Supply voltage: 6 to 18V Output current: 2A Output voltage: 0.8 to Vcc×0.9V

- P Operating frequency: 200 to 2500kHz Operating temperature: -40 to +85°C Reference voltage accuracy: ±2%

# Lower output ripple voltage Lower output ripple voltage 1.2 1.2 Compatible with smaller external coil and capacitor Coil 14 Capacitor 120 The above advantages are not applicable at the same time.

#### ROHM also offers a lineup of single-output switching regulators with built-in MOSFET

| Type                         | Part Number   | Supply Voltage(V) | Output Current(A) | Output Voltage(V) |

|------------------------------|---------------|-------------------|-------------------|-------------------|

| Simple<br>step-down          | BD9701 series | 8 to 35           | 1.5               | 1 to Vcc-3        |

|                              | BD9703 series | 8 to 35           | 1.5               | 1 to Vcc-3        |

|                              | BD9702 series | 8 to 35           | 3                 | 1 to Vcc-3        |

| Flexible                     | BD9001F       | 7 to 46           | 2                 | 1 to VIN          |

| step-down                    | BD9778 series | 5 to 35           | 2                 | 1 to VIN          |

|                              | BD9781HFP     | 5 to 35           | 4                 | 1 to VIN          |

| High-efficiency<br>step-down | BD9106FVM     | 4.0 to 5.5        | 0.8               | 1 to 2.5          |

|                              | BD9109FVM     | 4.5 to 5.5        | 0.8               | 3.3               |

|                              | BD9107FVM     | 4.0 to 5.5        | 1.2               | 1 to 1.5          |

| High-efficiency<br>step-up   | BD8158FVM     | 2.1 to 4          | 1.4               | Vcc to 14         |

|                              | BD8152FVM     | 2.5 to 5.5        | 1.4               | Vcc to 14         |

|                              |               |                   |                   |                   |

Excellence in Electronics

## WORLDWIDE SELECTION PERSONALIZED SERVICE

Access to over **540,000** part numbers from more than **320** quality, name-brand manufacturers!

#1 for Breadth of Product

**#1 for Availability of Product**

**#1 for On-Time Delivery**

**#1 for Overall Performance**

Source: EE Times Distributor Evaluation Study, September 2005

CORPORATION

1.800.344.4539

AME-DAY HIPMENT

www.digikey.com

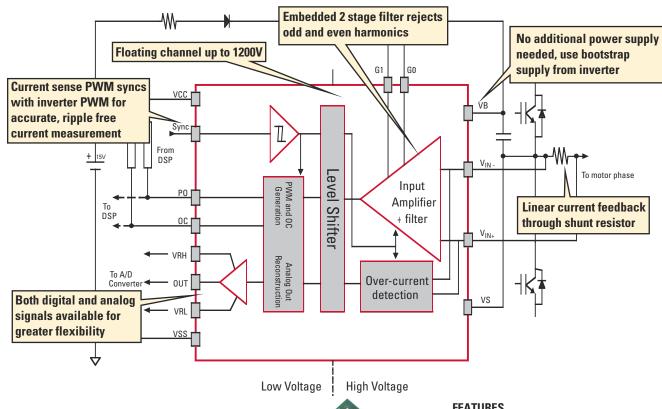

### RIPPLE & NOISE IMPEDING YOUR **MOTOR CURRENT SENSE?**

High Voltage IC Integrates 2-Stage Filter and PWM Sync for Accurate Current Measurement

#### MOTION **INTEGRATED DESIGN**

| Specifications                       | IR2175xPbF | IR2177xPbF  | IR2277xPbF  |

|--------------------------------------|------------|-------------|-------------|

| Floating channel voltage             | 600V       | 600V        | 1200V       |

| V <sub>IN</sub> range                | +/-260mV   | +/-250mV    | +/-250mV    |

| Carrier output frequency bandwidth   | 15kHz      | 20kHz       | 20kHz       |

| Over-current threshold               | +/-260mV   | +/-470mV    | +/-470mV    |

| Analog output dynamically adjustable | N/A        | Yes         | Yes         |

| Package                              | 8-pin SOIC | 16-pin SOIC | 16-pin SOIC |

| 2-Stage filter                       | No         | Yes         | Yes         |

| Bootstrap supply range               | 13-20V     | 8-20V       | 8-20V       |

| External sync                        | No         | Yes         | Yes         |

iMOTION is a trademark of International Rectifier.

#### **FEATURES**

- High speed, single phase current sense IC

- Suitable for DSP and analog-to-digital interface without additional external logic circuit

- Designed to avoid common mode dv/dt noise up to 50V/ns

- IR industry leading, high voltage technology

- · Single, rugged, compact IC

IR's ¿MOTION brings digital controllers, analog stage and power modules together in one easy to implement, integrated design platform.

Don't let poor performance spoil your designs. With high performance AVR® microcontrollers you can create applications with no worries about the microcontrollers performance. AVR Flash microcontrollers operate with clock rates up to 20 MHz, achieving close to 20 MIPS. With 32 general purpose registers, the AVR delivers unmatched performance and flexibility while reducing power consumption to a minimum.

Learn more and try to unmask the Super AVR at www.atmel.com/ad/superAVR

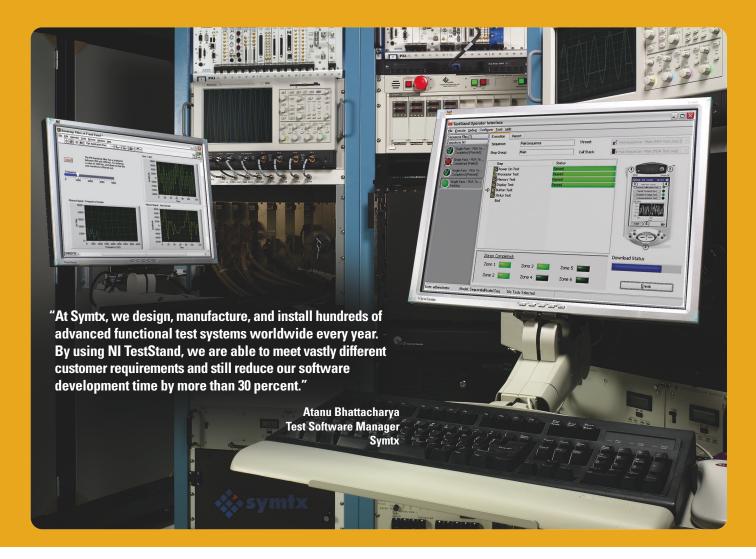

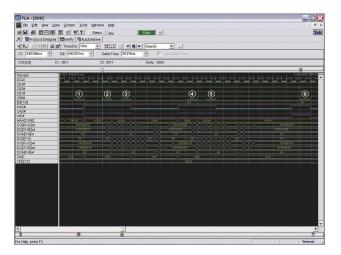

## NI TestStand – The Industry Standard in Test Management Software

NI TestStand is a ready-to-run test management environment from National Instruments for automating your test and validation systems. With NI TestStand you can:

- Develop, manage, and automate your test sequences

- Simplify your maintenance through a modular, fully customizable test-system framework

- Leverage toolkits and add-ons from NI TestStand product and solution partners

- Execute test modules written in any programming language

- Specify sequence flow, reporting, database logging, and connectivity to enterprise systems

- Maximize test throughput with built-in parallel and batch execution and synchronization

To learn how Symtx and other electronic manufacturers are accelerating development and reducing costs, visit ni.com/teststand.

(800) 891-8841

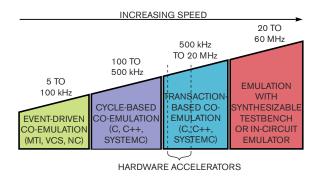

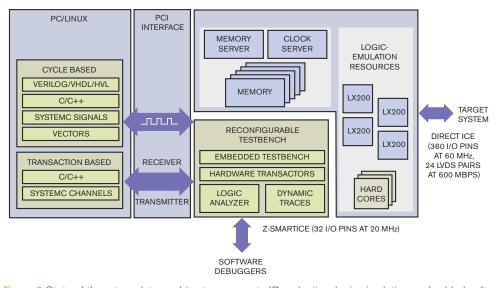

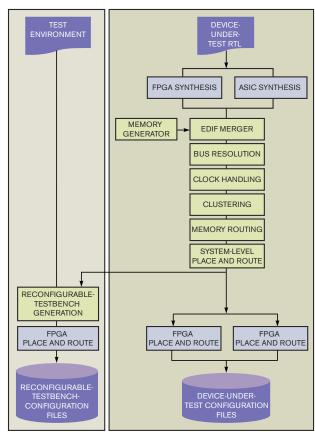

#### System architects get help from emulators

Emulators, which designers once used only for debugging at the last stages of design implementation and for regression testing, are now becoming useful tools for system architects, as well.

by Gabe Moretti, GABEonEDA

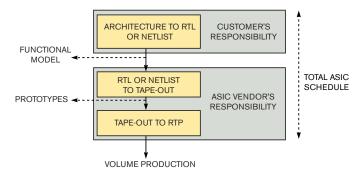

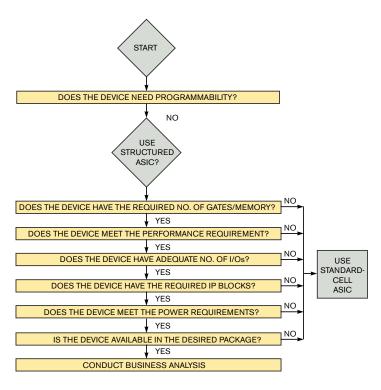

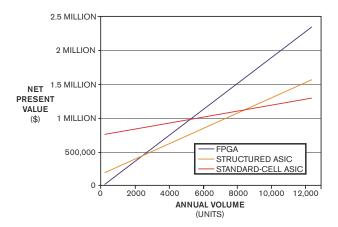

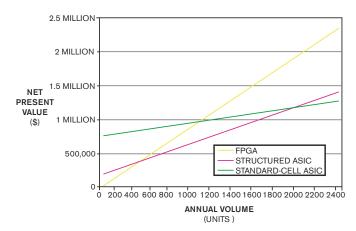

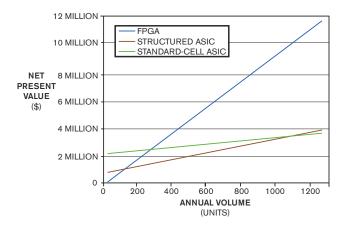

#### The economics of structured- and standard-cell-ASIC designs

Structured ASICs offer cost and performance that fall between FPGAs and traditional standard-cell ASICs. But their introduction has complicated the choice of the right silicon. by Arun Kottolli, Open-Silicon

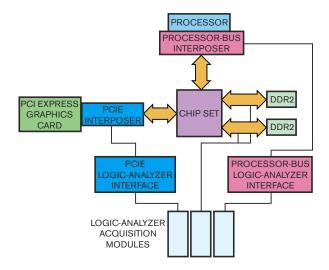

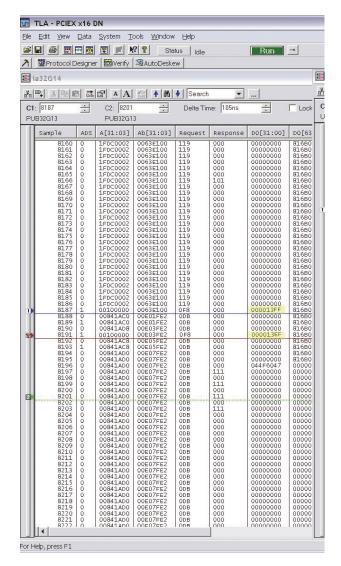

#### Mobile applications challenge test-andmeasurement tools

Advances in probing and triggering and in simultaneously monitoring multiple buses are adapting logic analyzers to the world of fast, low-power mobile applications. by Kris Utermark, Tektronix Inc.

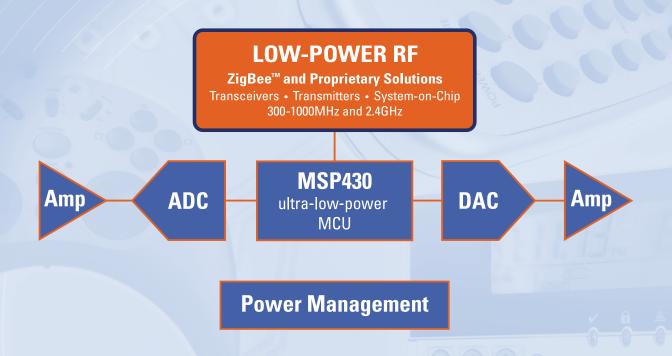

#### Wireless-sensor networks find a fit in the unlicensed band

Welcome to the new world of wireless connectivity, thanks to recently introduced standards, protocols, and enabling hardware for the unlicensed RF bands.

by Margery Conner, Technical Editor

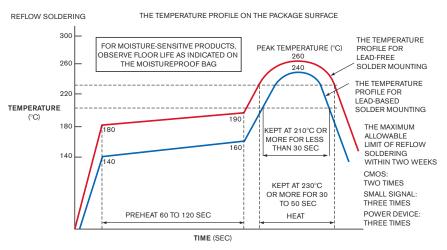

#### ROHS compliance: It's not easy being green

European environmental directives take effect soon, leaving many US companies struggling to overcome the challenges of implementing compliant designs.

by Richard A Quinnell, Contributing Technical Editor

#### SIGNIDEAS

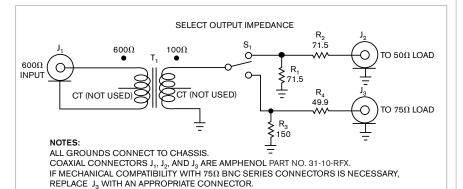

- 77 Audio-test accessory isolates and matches loads

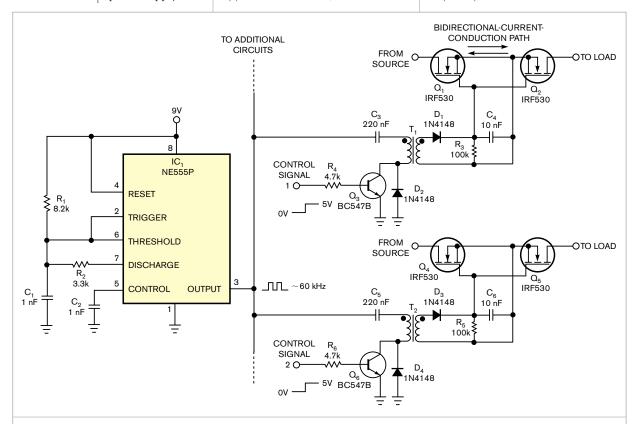

- 78 One oscillator drives multiple solid-state relays

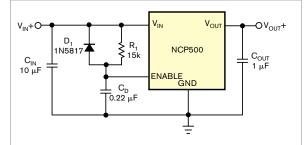

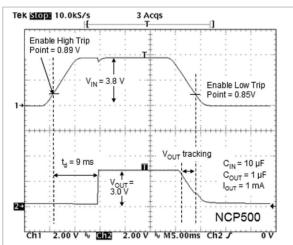

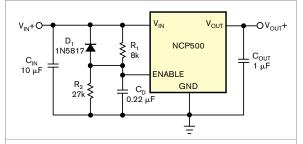

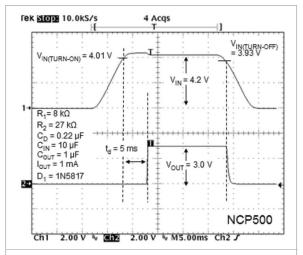

- 80 Low-dropout linear regulators double as voltage-supervisor circuits

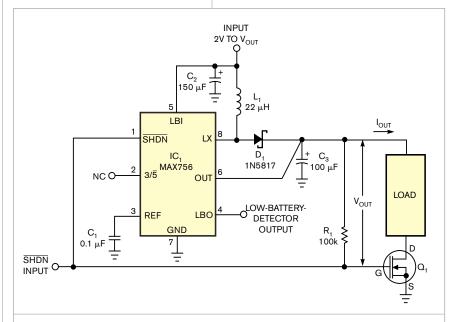

- External components provide true shutdown for boost converter

#### contents 3.16.06

- 21 Ultracapacitor family targets minimal series resistance and cost

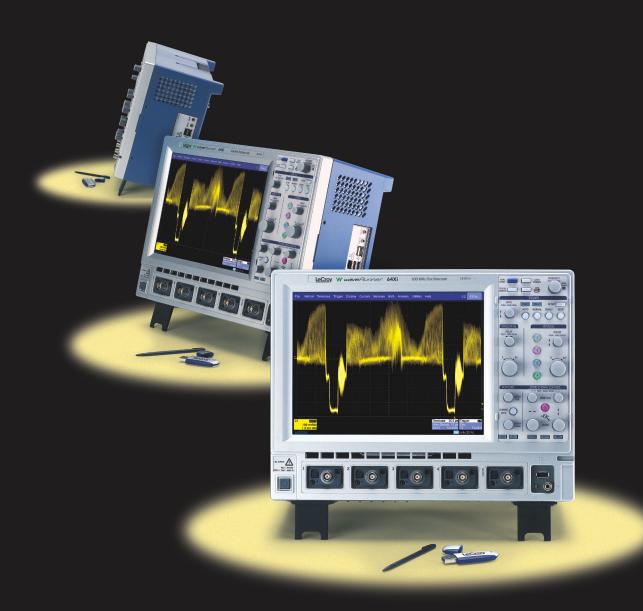

- 21 Platform captures, processes, displays broadband data

- 22 Cores lower entry cost for custom SOCs

- 24 Sigma-C and Mentor make strides in DFM

- 24 Thermal escalation drives need for controlled active cooling

- 26 **Voices:** Round table mulls hard-IP-at-board-level concept

- 28 Global Designer: Korea gets WiMax certification lab; Oscillator frequency pushes to 192 GHz for detection applications; SOC house partners with Malaysian fab; SOM concept adds versatility to embedded computing

## DEPARTMENTS & COLUMNS

- 14 **EDN.comment:** Slack EDA-market growth doesn't portend chip trends

- 32 **Bonnie Baker:** Choosing SAR versus high-speed delta-sigma ADCs

- 34 **Prying Eyes:** Figuring out the no-cost route

- 98 Reality Check: Game-console developer transforms itself

#### PRODUCT ROUNDUP

- Amplifiers, oscillators, and mixers: Class D, groundreferenced, CMOS, and operational amplifiers; transceiver family; and more

- 91 **Embedded Systems:** Microstepping drives, VME units, tool suites, and more

- 92 Integrated Circuits: Image-system controllers, processors, codecs, receivers, and more

EDN ® (ISSN#0012-7515), (GST#123397457, R.B.I. Intl Pub Mail #0280844) is published biweekly, 26 times per year, by Reed Business Information, 8878 Barrons Blvd, Highlands Ranch, CO 80129-2345. Reed Business Information, a division of Reed Elsevier Inc, is located at 360 Park Avenue South, New York, NY 10010. Tad Smith, Chief Executive Officer, Stephen Moylan, President, Boston Division. Periodicals postage paid at Littleton, CO 80126 and additional mailing offices. Circulation records are maintained at Reed Business Information, 8878 S Barrons Blvd, Highlands Ranch, CO 80129-2345. Telephone (303) 470-4445. POSTMASTER: Send address changes to EDN®, PO Box 7500, Highlands Ranch, CO 80163-7500. EDN® copyright 2006 by Reed Elsevier Inc. Rates for nonqualified subscriptions, including all issues: US, \$165 one year, (includes 796 GST, GST#123397457); Mexico, \$215 one year, includes 796 GST#123397457); Mexico 796 One year, includes 796 One year, includes 796 One year, includes 796 One year, includes 796 One y

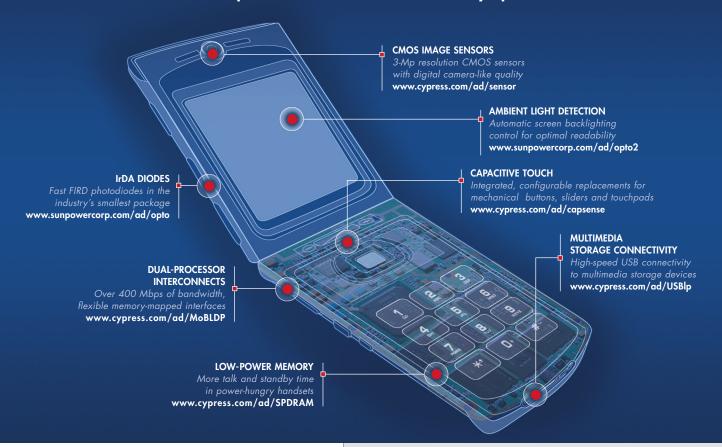

## Whatever your next innovative idea is, we'll help you design it.

Philips Nexperia Mobile Solutions. A mobile phone that can buy tickets to the game. A mobile phone that allows you to watch the game when you can't get to the stadium. A mobile phone that takes a picture of your friend coming to terms with his team's loss and shares it with your other friends. People buy their mobile phones today expecting much more than just a mobile phone. That's why you need an adaptable technology solution that can be tailored and changed as fast as your consumer needs. With Philips Nexperia Mobile Solutions, you'll find flexibility in platform design to customize your handset offering for different features and markets, and a total system approach that enables easy porting of various software applications. We address every type of GSM/GPRS/EDGE/UMTS/TD-SCDMA mobile phone, and provide expertise in value-added features such as connectivity, security, broadcast and multimedia. So no matter what's next in mobile phones, Philips will help you design it.

## ANALOG edge<sup>st</sup>

Expert tips, tricks, and techniques for analog designs

Vol. IV, Issue 3

#### **Intermediate Frequency (IF) Sampling Receiver Concepts**

Mark Rives, Principal Applications Engineer

his article will discuss Intermediate Frequency (IF) sampling concepts of sub-sampling (or under sampling), noise processing gain, and the effects of interfering signals. Examples will be based on the GSM/EDGE communications standard where the channel bandwidth is 200 kHz and the sample rate is typically a multiple of 13 MHz.

#### **Sub-Sampling**

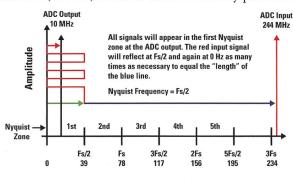

Nyquist's sampling theorem states that if a signal is sampled at least twice as fast as the highest sampled frequency component, no information will be lost when the signal is reconstructed. The sample rate divided by two (Fs/2) is known as the Nyquist frequency and the frequency range from DC (or 0 Hz) to Fs/2 is called the first Nyquist zone.

Input Frequency (MHz)

Figure 1. Nyquist Sampling Example

We'll use National's high-speed ADC12DL080 as an example. Clocking the ADC12DL080 at 6 \* 13 MHz or 78 Mega-Samples Per Second (MSPS) places the Nyquist frequency at 39 MHz. All the signal information that falls in the first Nyquist zone is over sampled and can be recovered. If the sampled signal moves into the second Nyquist

zone from 39 MHz to 78 MHz, it can still be recovered but the absolute frequency information is lost. When the input signal moves above Fs/2, it has been sub-sampled and 'reflects' or 'folds' at Fs/2 and moves back toward 0 Hz at the ADC output. If Fs/2 = 39 MSPS, an input signal at 40 MHz will fold back to 38 MHz. Folding will occur in each Nyquist zone. For example, a 244 MHz IF at 78 MSPS will result in a 10 MHz signal at the ADC output. The folded (or aliased) frequency is calculated by finding the closest multiple of Fs to the desired input frequency ( $F_{\rm IN}$ , 244 MHz), then subtracting the two frequencies:

$$F_{IN} = (n * Fs) \text{ or } 244 \text{ MHz} - (3 * 78 \text{ MHz})$$

= 244 MHz - 234 MHz = 10 MHz

Signals at 10 MHz, 68 MHz, 88 MHz, 146 MHz, and beyond will all appear at 10 MHz. There is no way to determine the original IF since the Nyquist criteria has been violated.

Sub-sampling systems take advantage of this folding or mixing function to reduce the IF frequency prior to a final digital tuner like National's CLC5903. If the desired signal Bandwidth (BW) is less than Fs/2, all of the signal information can still be recovered. A channel filter should be placed in front of the ADC to remove any undesired signals from other Nyquist zones. This filter will also limit the amount of noise at the ADC input to only one Nyquist zone.

#### **Noise Processing Gain**

As the ADC input frequency increases, the Signal-to-Noise Ratio (SNR) for large signals will decrease due to clock jitter. Small signal SNR is not affected. For the ADC12DL080, the large signal SNR will be 65 dBFS (dB relative to Full Scale) at a 244 MHz IF. When the

**NEXT ISSUE:**

**Extending Power-over-Ethernet**

#### **Featured Products**

#### ADC12DL080 Dual, 12-bit, 80 MSPS Analog-to-Digital Converter for High-IF Sampling

The ADC12DL080 is a dual, low-power monolithic CMOS analog-to-digital converter. This device is capable of converting an analog input signal into 12-bit digital words at rates up to 80 Mega-Samples Per Second (MSPS). The ADC12DL080 is designed with 600 MHz full-power input bandwidth and low aperture jitter to allow sampling of high-frequency IF inputs. Operating on a single 3.3V supply, the ADC12DL080 achieves 11.0 effective bits at Nyquist and consumes just 450 mW at 80 MSPS. A power-down feature reduces power consumption to 100 mW.

The ADC12DL080 may be used either with an external reference voltage (1.0V nominal, 0.8V to 1.5V allowed) or with an internal precision 1.0V ref-

erence. The differential inputs provide a full-scale differential input swing equal to two times the reference voltage with the possibility of a single-ended input. Duty cycle stabilization is applied to the input clock to provide an internal duty cycle of 50%. The output data can be set for offset binary or two's complement.

#### **Features**

- Single 3.3V supply operation

- Outputs 2.4V to 3.6V compatible

- Low power consumption

- Power-down mode

- Duty cycle stabilizer

- External or internal selectable reference

- Pin-compatible with ADC12DL040, ADC12DL065, and ADC12DL066

For input frequencies as high as 200 MHz, the ADC12DL080 provides an impressive 67 dB SNR and 81 dB SFDR, making it ideal for high-IF sampling receivers, test and measurement equipment, radar, and medical imaging applications. The ADC12DL080 is offered in a TQFP-64 package and operates over the industrial temperature range of -40°C to +85°C.

For FREE samples, datasheets, and more, visit www.national.com/pf/DC/ADC12DL080.html

### ADC12DL040/65 Dual, 12-Bit A/D Converters for Excellent Signal Conditioning and Acquisition

The ADC12DL040 and ADC12DL065 are dual, low-power 12-bit Analog-to-Digital Converters (ADC) capable of converting analog input signals at 40 and 65 Mega-Samples Per Second (MSPS), respectively. These ADCs provide excellent dynamic performance and 250 MHz full-power bandwidth. The ADC12DL040 achieves 11.1 effective bits and consumes just 210 mW at 40 MSPS and the ADC12DL065 achieves 11.0 effective bits and consumes 360 mW at 65 MSPS.

The differential inputs provide a full-scale differential input swing equal to two times the reference voltage with the possibility of a single-ended input. The digital outputs from the two ADCs are available on a single multiplexed 12-bit bus or on two separate buses. Duty cycle stabilization is applied to the input clock to provide an internal duty cycle of 50%. The output data can be set for offset binary or two's complement.

#### **Features**

- Single 3.0V (ADC12DL040) and 3.3V (ADC12DL065) supply operation

- Internal reference

- Outputs 2.4V to 3.6V compatible

- Low power consumption

- Power-down mode

- Duty cycle stabilizer

- Multiplexed output mode

The ADC12DL040/65 provide an impressive 68.5 dB SNR and 85 dB SFDR at Nyquist while consuming just 210 mW and 360 mW, respectively. These converters are ideal for portable instrumentation, medical imaging, communications receivers, and wireless infrastructure equipment. These ADCs are available in TQFP-64 packaging and operate over the industrial temperature range of -40°C to +85°C.

For FREE samples, datasheets, and more, visit www.national.com/pf/DC/ADC12DL040.html www.national.com/pf/DC/ADC12DL065.html

#### **IF Sampling Receiver Concepts**

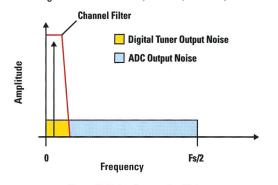

input is reduced to -10 dBFS or less, the SNR will increase to 70 dBFS. If the desired channel bandwidth is over sampled, a digital channel filter can further improve the SNR. When an ADC's SNR is measured, it is normally specified as the SNR in the first Nyquist zone. In other words, all the noise from DC to Fs/2 is summed to get the SNR relative to the ADC's full-scale input. A digital channel filter can remove the ADC output noise except in the channel bandwidth. The output noise is integrated over a smaller frequency range. This improvement is called noise processing gain and can be calculated with the following equation:

Processing Gain = -10 \* LOG (Channel BW/Nyquist BW)

For a 200 kHz narrow-band system:

Processing Gain = -10 \* LOG (200 kHz/39 MHz) = 22.9 dB

Figure 2. Noise Processing Gain

Processing gain can also be calculated by finding the noise floor of the ADC in dBm/Hz. With an IF of 244 MHz at -1 dBFS, the SNR of the ADC12DL080 is 65 dBFS or -55 dBm since full scale is +10 dBm into  $50\Omega$ . To translate into dBm/Hz, take 10 \* LOG (Fs/2) and subtract it from -55 dBm. 10 \* LOG (39 MHz) = 75.9 dB, therefore the ADC12DL080 noise floor in this example is -130.9 dBm/Hz. Now if the channel bandwidth is 200 kHz, add back 10 \* LOG (200 kHz) or 53 dB to get a noise floor of -77.9 dBm in 200 kHz, which is 22.9 dB better than the ADC by itself. Translating back to dBFS, the total SNR is 87.9 dB in a 200 kHz channel. This is similar to decreasing the resolution bandwidth on a spectrum analyzer; the noise floor has been lowered, but the ADC's resolution has not been increased.

#### **Interfering Signals**

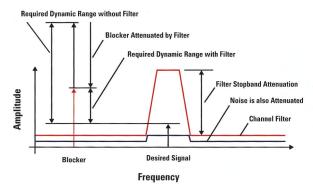

GSM systems require the receiver to operate with signals from -13 dBm to -104 dBm when there are no interfering signals. Typical receivers need some extra margin to demodulate the received signal. This is called the Carrier-to-

Interferer (C/I) ratio and is 9 dB for GSM. This means that the noise floor must be below -113 dBm, resulting in a dynamic range of greater than 100 dB, which is more than our ADC can provide. Normally a Variable Gain Amplifier (VGA) is added to the system to scale the input signal to the ADC.

Adding a VGA works well until a large interfering signal is present. In GSM systems, this condition can occur when one subscriber is close to the basestation and one is far away. The close subscriber may actually be talking to a more distant basestation on an adjacent channel, which can block the reception of the weak signal. Hence, the large signal is known as a blocker. The blocker can be up to -13 dBm while the weak signal can be as low as -101 dBm. Considering the 9 dB C/I ratio, the overall dynamic range requirement is now -13 dBm – (-110 dBm) or 97 dB with a blocking signal. If the blocker causes the VGA gain to decrease to prevent clipping the ADC input, the weak signal can be lost in the noise.

The channel filter in front of the ADC will reduce the level of the blocking signal, but the ADC will still operate near full scale. Clock jitter and the large signal will degrade the SNR causing a loss of sensitivity if the filter rejection of the blocker is not sufficient.

Figure 3. Channel Filter

#### Summary

High-speed ADCs such as the ADC12DL080 combined with a digital tuner such as the CLC5903 can simplify receiver design and provide excellent performance for high dynamic range signals. More information on this topic is available in the user's guide for the CLC-LDRCS-PCASM evaluation board at www.national.com/store#DataAcquisition.

#### **Featured Products**

#### **Differential, High-Speed Op Amps**

The LMH6550 and LMH6551 are high-performance voltage feedback differential amplifiers. The fully differential topology allows balanced inputs to the ADCs and can be used as

single-ended-to-differential or used as differential-to-differential. These amplifiers also have the high speed and low distortion necessary for driving high-performance ADCs, as well as the current-handling capability to drive signals over balanced transmission lines like CAT-5 data cables.

With external gain set resistors, the LMH6550/51 can be used at any desired gain. Gain flexibility coupled with high speed makes these amplifiers suitable for use as IF amplifiers in high-performance communications equipment.

#### LMH6550 Features

- 400 MHz, -3 dB Bandwidth  $(V_{OUT} = 0.5 V_{P-P})$

- 90 MHz, 0.1 dB Bandwidth

- -92/-103 dB HD2/HD3 at 5 MHz

- 3000 V/µs Slew rate

- -68 dB Balance error (V<sub>OLIT</sub> = 1.0 V<sub>P-P</sub>, 10 MHz)

- 10 ns Shutdown/enable

#### LMH6551 Features

- 370 MHz, -3 dB Bandwidth  $(V_{OUT} = 0.5 V_{P-P})$

- 50 MHz, 0.1 dB Bandwidth

- -94/-96 dB HD2/HD3 at 5 MHz

- 2400 V/µs Slew rate

- -70 dB Balance error  $(V_{OUT} = 0.5 V_{P-P}, 10 MHz)$

- Single +3.3V, +5V, or ±5V supply voltages

The LMH6550/51 are ideal for use in applications requiring a differential A/D driver, video twisted pair, differential line driver, single-ended-to-differential converter, high-speed differential signaling, IF/RF amplifier, or SAW filter buffer/driver.

The LMH6550/51 are available in the space-saving SOIC-8 and MSOP-8 packaging.

For FREE samples, datasheets, and more, visit www.national.com/pf/LM/LMH6550.html www.national.com/pf/LM/LMH6551.html

#### ADC14L020/40 14-Bit, 20 and 40 MSPS ADCs

The ADC14L020 and the ADC14L040 are low-power, monolithic 14-bit 20 and 40 Mega-Samples Per Second (MSPS) Analog-to-Digital Converters (ADC). These ADCs provide excellent dynamic performance and 150 MHz full-power bandwidth. The ADC14L020 achieves 12.0 effective bits and consumes 150 mW at 20 MSPS. The ADC14L040 achieves 11.9 effective bits and consumes 235 mW at 40 MSPS. The power-down feature on both products reduces power consumption to 15 mW.

The differential inputs provide a full-scale differential input swing equal to two times the reference voltage with the possibility of a single-ended input. Duty cycle stabilization is applied to the input clock to provide an internal duty cycle of 50%. The output data can be set for offset binary or two's complement.

To ease interfacing to lower voltage systems, the digital output driver power pins of the ADC14L020/40 can be connected to a separate supply voltage in the range of 2.4V to the analog supply voltage.

#### **Features**

- Single 3.3V supply operation

- Outputs 2.4V to 3.6V compatible

- Low power consumption

- Duty cycle stabilizer

- Internal reference

- Power-down mode

The ADC14L020/40 provide an impressive 74 dB SNR and 93 dB SFDR at Nyquist while consuming just 150 mW, making them ideal for portable medical imaging, instrumentation, home gateways, and communications receivers. These converters are available in LQFP-32 packages and operate over the industrial temperature range of -40°C to +85°C.

For FREE samples, datasheets, and more, visit www.national.com/pf/DC/ADC14L020.html www.national.com/pf/DC/ADC14L040.html

## ED online contents

#### ONLINE ONLY

Check out these online-exclusive articles.

#### With integrated RF, you need a relationship, not a foundry

Design decisions: Atheros Communications depends on its foundry to hold stable the process parameters that impact RF-model parameters.

www.edn.com/article/CA6309406

#### JEDA offers ESL assertion tool

Verification vendor JEDA Technologies is expanding its IC-verification portfolio with a tool called NSCa (Native SystemC Assertion).

www.edn.com/article/CA6309146

#### Tool supports OPC reuse

DFM start-up Aprio Technologies is adding a third offering to its OPC (optical-proximity-correction) tool lineup with features for creating OPC libraries and for viewing, during IC design, what parts of a layout will print properly in manufacturing.

www.edn.com/article/CA6308638

#### The square root of the sum of the squares

To generate an analog voltage the proportional to the module of a vector whose components are also available in analog form, you can update a 40-year-old approach.

www.edn.com/article/CA6312102

#### INNOVATION AWARDS

Join us to honor innovation. You voted in our annual Innovation program, and we'll be announcing the winners April 3 in San Jose. Visit the **Innovation page to** review the finalists, get information about the awards dinner, and buy tickets.

www.edn.com/ innovation

#### READER'S CHOICE

A selection of recent articles receiving high traffic on www.edn.com.

#### The hot 100 products of 2005

Featuring an audio introduction by Editor in Chief Maury Wright.

www.edn.com/article/ CA6290449

#### Using Mathcad to derive circuit equations and optimize circuit behavior

The general-purpose mathematical-analysis tool provides ample capabilities that engineers can employ in circuit design.

www.edn.com/article/ CA6301377

#### Build a USB-based GPIB controller

Roll-your-own USB-based instrumentation bus.

www.edn.com/article/ CA6290453

#### Tales from the Cube: Hardware designer on an electric chair

Mysterious spikes—with immense amplitudes of about 2V-appeared every now and then on the control lines. Could the spikes be the reason for the sporadic interface failure?

> www.edn.com/article/ CA6301636

#### CMOS inverters convert RF to digital signal

Hex-inverter-based design suits frequencies up to 180 MHz.

> www.edn.com/article/ CA6294159

#### FROM THE VAULT

Articles and extras from the EDN archives that relate to this issue's contents.

#### WIRELESS-SENSOR NETWORKS FIND A FIT IN THE UNLICENSED BAND (pg 46):

#### Mesh-network platform promises 99.9% reliability for remote monitoring

Dust Networks claims its mesh platform provides the highest system reliability available-along with the lowest power consumption.

→ www.edn.com/article/CA6277105

#### Low-rate networks take control: Rest assured

As businesses strive to increase efficiency and reduce labor costs through automation, low-data-rate networks are poised to become the workhorses of the wireless world.

→ www.edn.com/article/CA443378

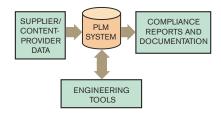

#### ROHS COMPLIANCE: IT'S NOT EASY BEING GREEN (pg 37): Design software complies with ROHS

ROHS features are popping up in pc-board-design software.

→ www.edn.com/article/CA6280047

#### CHOOSING SAR VERSUS HIGH-SPEED DELTA-SIGMA ADCs (pg 32):

#### High-speed ADCs: preventing front-end collisions

Performance advances in communication technologies, imaging, instrumentation, and other data-dense applications critically depend on high-speed ADCs.

→ www.edn.com/article/CA415122

#### BY MAURY WRIGHT. EDITOR IN CHIEF

## Slack EDA-market growth doesn't portend chip trends

less-than-stellar record of recent growth in the EDA industry has been a hot topic. Clearly, such trends matter greatly to the companies that sell EDA tools. But, too often, observers relate tough times in the EDA market to potential softness in the semiconductor business. That link is tenuous at best. In fact, a recent DesignCon panel that set out to discuss stagnant EDA growth ended up

pointing out just how big the separation between EDA and the semiconductor industry can be.

In a panel called "Why is EDA stagnating, or is it?" the group quickly agreed that the market was stagnant and even why that's so. Richard Tobias, vice president of engineering at Pixelworks, stated, "We need innovation in ESL [electronic-system level] and DFM [design for manufacturing]. The core place and route [segment] is stagnating."

Gary Smith, vice president and chief analyst at Gartner Dataquest, agreed. Smith pointed out that an increasing number of design engineers are now using tools developed in-house. Smith pegged the number of such users at 27%, whereas he claimed only about 10 to 12% of "power users" have relied on in-house tools in the past. Smith claimed that the trend is largely due to the lack of commercially available ESL tools. For more details centric to the EDA industry, check out the information in **Reference 1**.

Although I found the EDA-industry discussion interesting, I found the insights into the semiconductor market even more fascinating. Indeed, although ESL and DFM may enable innovations in semiconductors, the semiconductor industry drives EDA.

A couple of the panelists made statements about the chip business that both help explain the slow EDA segment and run counter to themes from the EDA crowd. Len Perham, chairman of Optimal, for instance, challenged the notion that ASIC-design starts will continue to decline. Perham basically questioned how we can have an explosion of compelling new consumer products while the chip industry designs fewer ICs. And, Perham was quick to warn that the bulk of the design activity may not be at the leading-edge process nodes. On the subject of process, he stated, "0.11 micron is going to have a very long life."

Tobias of Pixelworks made a similar point. He claimed that, even in instances in which a design team does an SOC (system on chip) in, say, a 90-nm process, support chips might use a trailing-edge 180-nm process.

I also believe that many designs will stay at 130-nm and less dense geometries (Reference 2). There is no question that PC processors, memory, FPGAs, and handset chips can benefit from the latest process. Most other designs would benefit from the less complex design issues at 130 nm and

above. And I bet that this trend is having some effect on EDA growth. Design teams that stay at 130 nm and above don't need new tools.

Of course, the question remains concerning why analysts continue to report a drop in ASIC-design starts. I don't have an answer. But I've always wondered how EDA companies and analysts alike count the ASSPs (application-specific standard products) that fabless-semiconductor companies develop. Those designs rely on the same tools and travel through fabs in the same way as an ASIC that an OEM-design team develops. Does it count as an ASIC-design start when a merchant semiconductor company does an ASSP? I've yet to get consistent answers to that question.

Panelist Jim Hogan, general partner at Telos Venture Partners, did note, "There are a lot of design starts that aren't even measured." **EDN**

Contact me at mgwright@edn.com.

#### REFERENCES

- Mutschler, Ann Steffora "Help wanted: ES level evangelist to drive EDA growth," *Electronic News*, Feb 8, 2006, www.reed-electronics.com/electronicnews/article/CA6305703.

- Wright, Maury, "Are cell-based ASICs going away?" *EDN*, Dec 5, 2005, pg 14, www.edn.com/article/CA6288036.

#### MORE AT EDN.COM

$\triangleright$

+ Go to www.edn.com/060316ed1 and click on Feedback Loop to post a comment on this editorial.

Thermal

Thermal Magnetic

Magnetic

High Performance

Electronic

## **3120-F7**Applications include: marine, medical and office equipment, appliances and tools.

## No two circuit breaker applications are alike

## Only E-T-A offers more technologies

Many circuit protection applications appear the same but every application is different requiring a specific circuit protection solution. Only E-T-A provides the most complete range of available circuit protection technologies.

More technologies allow for superior, more precise circuit protection. It is critical that your design is protected with the correct circuit protection. Your reputation depends on it.

One call to E-T-A will ensure your design has the right circuit protection technology to enhance your products safety, reliability and brand reputation.

Go to www.e-t-a.com/ipod1 for your chance to win one of 10 video iPods®

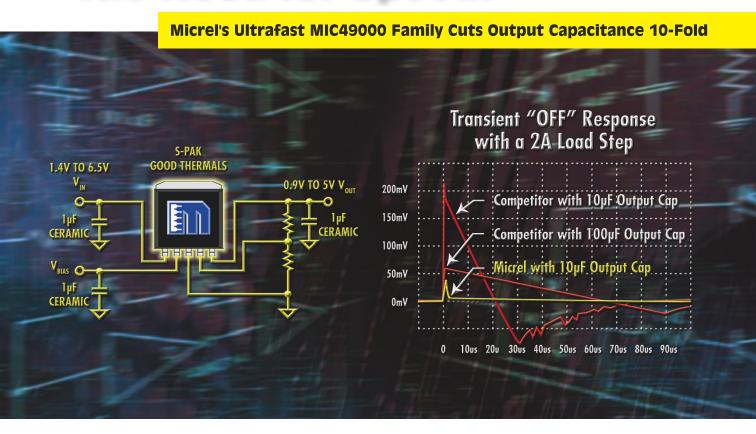

## The Need for Speed!

Any designer can tell you; fast is no longer fast enough. State of the art CPUs, ASICs and FPGAs used in PC, server, networking, communication and graphic card applications require the fastest possible transient response. The ultra-fast bandwidth of Micrel's MIC49000 family enables well regulated output with minimal output capacitance. Competitor products require up to 10 times the capacitance which increases the cost and size of the solution.

With 1.5A, 2A, 3A and 5A output current ratings, the MIC49000 family is ideal for a broad range of applications.

For more information, contact your local Micrel sales representative or visit us at: www.micrel.com/ad/mic49000. Literature: 1 (408) 435-2452 Information: 1 (408) 944-0800

#### The Good Stuff:

- ◆ Ultra-fast transient response: 10MHz gain-bandwidth

- Very low dropout

- Wide input voltage range:

- Vin: 1.4V to 6.5V

- ❖ Vbias: 3.0V to 6.5V

- Tiny output capacitor stable with only 1μF ceramic output capacitor

- ◆ Logic enable input

- ◆ Current limit and thermal shutdown protection

- ◆ 40°C to +125°C junction temperature range

#### www.micrel.com

#### **Specifications**

| Part Number | Package              | I <sub>OUT</sub> (A) | V <sub>out</sub> Options | V <sub>IN</sub> Range | V <sub>DROPOUT</sub> TYP (mV)<br>@ I <sub>MAX</sub> |

|-------------|----------------------|----------------------|--------------------------|-----------------------|-----------------------------------------------------|

| MIC49150    | Power MSOP-8/S-PAK-5 | 1.5                  | 0.9, 1.2, 1.5, 1.8 Adj.  | 1.4V to 6.5V          | 280                                                 |

| MIC49200    | S-PAK-5              | 2                    | 1.0, 1.8, Adj.           | 1.4V to 6.5V          | 400                                                 |

| MIC49300    | S-PAK-5              | 3                    | 0.9, 1.2, 1.5, 1.8 Adj.  | 1.4V to 6.5V          | 280                                                 |

| MIC49500    | S-PAK-7, TO-263-7    | 5                    | 0.9, 1.2, Adj.           | 1.4V to 6.0V          | 290                                                 |

#### PUBLISHING DIRECTOR, EDN WORLDWIDE

John Schirmer

1-408-345-4402; fax: 1-408-345-4400 jschirmer@reedbusiness.com

#### EDITOR IN CHIEF

Maury Wright 1-858-748-6785 mgwright@edn.com

#### EXECUTIVE EDITOR

Ron Wilson 1-408-345-4427 ronald.wilson@reedbusiness.com

#### MANAGING EDITOR

Kasey Clark Contact for contributed technical articles 1-781-734-8436; fax: 1-781-290-3436 kase@reedbusiness.com

#### EXECUTIVE EDITOR, ONLINE

Matthew Miller 1-781-734-8446; fax: 1-781-290-3446; mdmiller@reedbusiness.com

#### SENIOR ART DIRECTOR

Mike O'Leary 1-781-734-8307; fax: 1-781-290-3307; moleary@reedbusiness.com

#### EMBEDDED SYSTEMS

Warren Webb, Technical Editor; 1-858-513-3713; fax: 1-858-486-3646 wwebb@edn.com

#### ANALOG/COMMUNICATIONS. DISCRETE SEMICONDUCTORS

Maury Wright, 1-858-748-6785; mgwright@edn.com

#### EDA. MEMORY.

PROGRAMMABLE LOGIC Michael Santarini, Senior Editor;

1-408-345-4424 michael.santarini@reedbusiness.com

#### MICROPROCESSORS, DSPs. TOOLS

Robert Cravotta, Technical Editor; 1-661-296-5096; fax: 1-781-734-8070 rcravotta@edn.com

#### MASS STORAGE, MULTIMEDIA,

PCs AND PERIPHERALS

Brian Dipert, Senior Technical Editor; 1-916-760-0159; fax: 1-781-734-8038; bdipert@edn.com

#### POWER SOURCES. ONLINE INITIATIVES

Margery Conner, Technical Editor 1-805-461-8242; fax: 1-805-461-9640; mconner@connerbase.com

#### DESIGN IDEAS EDITOR

**Brad Thompson** edndesignideas@reedbusiness.com

#### SENIOR ASSOCIATE EDITOR

Frances T Granville, 1-781-734-8439; fax: 1-781-290-3439; f.granville@reedbusiness.com

#### ASSOCIATE EDITOR

Maura Hadro Butler, 1-908-928-1403; mbutler@reedbusiness.com

#### **EDITORIAL AND ART PRODUCTION**

Diane Malone, Manager; 1-781-734-8445; fax: 1-781-290-3445 Steve Mahoney, Production Editor 1-781-734-8442: fax: 1-781-290-3442 Adam Odoardi, Prepress Manager 1-781-734-8325; fax: 1-781-290-3325

#### CONTRIBUTING TECHNICAL EDITOR

Dan Strassberg, strassbergedn@att.net

#### COLUMNISTS

Howard Johnson, PhD Bonnie Baker; Joshua Israelsohn

#### PRODUCTION

Dorothy Buchholz, Group Production Director 1-781-734-8329 Kelly Brashears, Production Manager 1-781-734-8328; fax: 1-781-734-8086 Linda Lepordo, Production Manager 1-781-734-8332; fax: 1-781-734-8086 Pam Boord, Advertising Art 1-781-734-8313; fax: 1-781-290-3313

#### EDN EUROPE

Graham Prophet, Editor, Reed Publishing The Quadrant, Sutton, Surrey SM2 5AS +44 118 935 1650; fax: +44 118 935 1670; gprophet@reedbusiness.com

#### EDN ASIA

Raymond Wong, Managing Director/ Publishing Director raymond.wong@rbi-asia.com Kirtimaya Varma, Editor in Chief kirti.varma@rbi-asia.com

#### EDN CHINA

William Zhang, Publisher and Editorial Director wmzhang@idg-rbi.com.cn John Mu. Executive Editor johnmu@idg-rbi.com.cn

#### EDN JAPAN

Katsuya Watanabe, Publisher k.watanabe@reedbusiness.jp Kenji Tsuda, Editorial Director and Editor in Chief tsuda@reedbusiness.ip Takatsuna Mamoto, Deputy Editor in Chief t.mamoto@reedbusiness.ip

The EDN Editorial Advisory Board serves as an industry touchstone for the editors of EDN worldwide, helping to identify key trends and voicing the concerns of the engineering community

#### **DENNIS BROPHY**

Director of Business Development Mentor Graphics

#### DANIS CARTER

Principal Engineer, Tyco Healthcare

#### CHARLES CLARK

Technical Fellow, Pratt & Whitney Rocketdyne

#### DMITRII LOUKIANOV System Architect, Intel

RON MANCINI

Staff Scientist, Texas Instruments

#### GABRIEL PATULEA

Design Engineer, Cisco

#### MIHIR RAVEL

VP Technology, National Instruments DAVE ROBERTSON

Product Line Director, Analog Devices

#### SCOTT SMYERS

VP Network and System Architecture Division, Sonv

#### TOM SZOLYGA

Program Manager, Hewlett-Packard

#### JIM WILLIAMS

Staff Scientist, Linear Technology

EDN. 225 Wyman St, Waltham, MA 02451. www.edn.com. Phone 1-781-734-8000; fax: 1-781-734-8070. Address changes or subscription inquiries: phone 1-800-446-6551; fax: 1-303-470-4280;

subsmail@reedbusiness.com. For a free subscription, go to www.getfreemag.com/edn. Reed Business Information, 8878 S Barrons Blvd, Highlands Ranch, CO 80129-2345. Include your mailing label.

#### No two circuit breaker applications are alike

#### Only E-T-A offers more technologies

#### ESS20-1

Prevent an overload on one circuit from shutting down the entire production line. Designed for switch-mode power supplies. www.e-t-a.com/ess2oedn

#### E-1048-800

Remote power controller utilizes "SMART" circuit protection technology. Circuit breaker, relay, analog output, and diagnostics in a single unit

www.e-t-a.com/e1048edn

Miniature Flow Monitor operates on the calorimetric principle and is designed to operate with air or inert gases. www.e-t-a.com/sw112edn

WWW.E-T-A.COM 1-800-462-9979

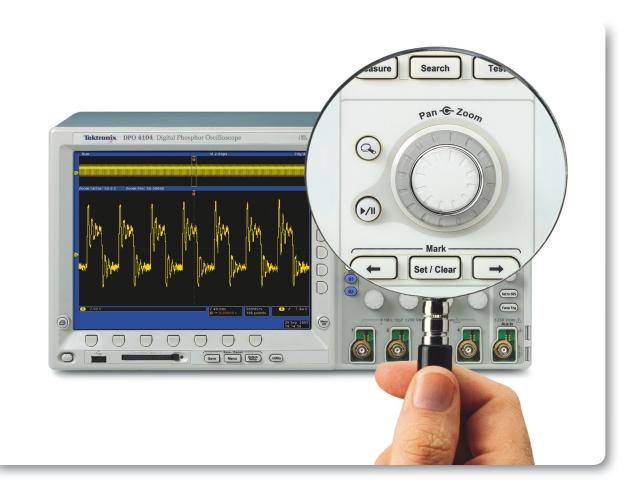

## Meet the Wave Inspector. Solve debugging challenges in record time.

Debug faster and easier than ever before with Wave Inspector™ in the new DPO4000 Series oscilloscopes. Now you can zoom, pan, play, pause, set, and clear waveform marks and even search for user-defined events using simple, dedicated front-panel controls. Combine that with integrated serial triggering and packet-level decoding on I<sup>2</sup>C, SPI, and CAN buses, and you've got a serious breakthrough in the complicated task of embedded systems debug. All in a deceptively small box that delivers outstanding performance. Start solving.

You've never seen anything like it. See for yourself. www.tektronix.com/newdpo4000

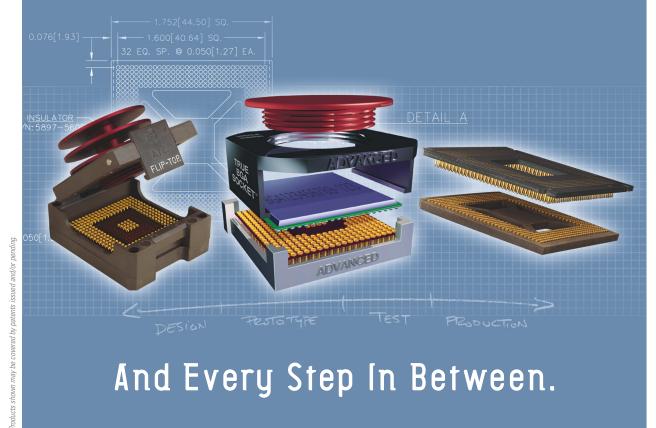

And Every Step In Between.

From concept to completion, Advanced is your *single* source for comprehensive BGA socketing systems. We specialize in economical, dependable alternatives to direct device attach, with an array of innovative solutions for any stage of development. Whether you're using BGA, LGA or CSP devices in prototype or production applications — you can be sure we're with you every step of the way.

To learn more, visit us online at http://www.bgasockets.com or call 1.800.424.9850.

5 Energy Way, West Warwick, Rhode Island 02893 USA

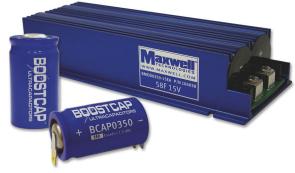

## Ultracapacitor family targets minimal series resistance and cost

Itracapacitors, also sometimes called supercapacitors or electric double-layer capacitors, have long offered promise in power applications alongside of and in place of batteries. The products can handle a million charge/discharge cycles and can provide a power boost for engine and motor starts in applications ranging from consumer electronics to hybrid vehicles. But cost has hampered the adoption of the technology. Last year, Maxwell Technologies introduced one ultracapacitor cell—the 2600F MC2600—that brought the price of the technology to 1 cent per farad. Now, the company is expanding the low-cost offering in cells ranging from 650 to 3000F and in modules that gang multiple cells.

The new members of the Boostcap family are cells and modules for either power or energy applications. Power applications include hybrid vehicles, distributed power systems, and others that demand the lowest possible series resistance. The energy line uses a lower cost electrode with higher series resistance and typically serves in roles such as battery backup or as a sporadic current boost in telecom systems to automatic meter-reading

Available both in individual cells and in multicell modules, the Boostcap family of ultracapacitors targets applications such as a motor-start power source in hybrid vehicles.

systems. The new family represents a better than halving of the cost of the earlier Boostcap family that the company announced four years ago.—by Maury Wright

▶ Maxwell Technologies, www.maxwell.com.

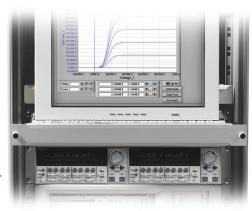

#### Platform captures, processes, displays broadband data

argeting transceiver applications, such as military radios and commercial wireless base stations, Pentek recently introduced the VME-based RTS 2502 development platform for real-time wideband-data acquisition, signal processing, and recording. The combination of data-recording and -playback capabilities in a single unit allows developers to capture and generate signals in real time for validation of signal-processing algorithms and system hardware.

Each 6U VME card in an RTS 2502 system accepts signals through two 14-bit ADCs operating as fast as 105 MHz and passes the signals

through digital downconverters to Virtex-II FPGAs for signal processing and data handling. The unit can send raw or processed data to a disk array at speeds as high as 160 Mbytes/sec for recording, and the unit can also send the data off-board through an FPDP (front-panel data port), a Race++ port, or a Gigabit Ethernet port.

Pentek's RTS 2502 transceiverdevelopment platform offers realtime, wideband-data recording and playback.

Two playback channels each offer digital upconversion and dual 500-MHz, 16-bit DACs to produce either real or I/Q RF signals, drawing data from other I/O or the disk array at speeds as high as 160 Mbytes/sec.

Pentek's GateFlow FPGA-design kit includes design information, software files, optimized DSP functions, and development utilities. The company's SystemFlow software includes API (application-programming-interface) libraries for the target board, as well as control libraries for the host PC. The software package also includes a data viewer,

written in LabView, that displays collected data in either the time or the frequency domain. Prices for the RTS 2502 system start at \$29,995 for hardware only and \$41,495 with bundled SystemFlow and GateFlow software.—by Warren Webb

Pentek Inc, www.pentek.com.

## Cores lower entry cost for custom SOCs

ensilica based its new Diamond Standard family of processor configurations on the Xtensa architecture. Each core implements the Xtensa instruction-set architecture in a five-stagepipeline, 32-bit architecture. The cores support modeless switching between 16- and 24-bit instructions to deliver high code density, high processing performance, and low power consumption. These processors offer a lower price to design teams considering the Tensilica technology. The company's Diamond Standard family includes six processor configurations.

The family comprises the 108Mini, a cacheless RISC-controller processor, which delivers lower power consumption than ARM7-based approaches. The smallest device in the family, the 108Mini uses a 0.38-mm² cell area in a 0.13-micron process and consumes 0.06 mW/MHz with the 0.13LV libraries or 0.09-mW/MHz with the 0.13G libraries.

The low-power, 24-bit Diamond 330HiFi audio processor supports audio and speech codecs; Tensilica based it on the Xtensa HiFi 2 audio engine. It supports decoding and

encoding for Dolby Digital AC-3, MP3, aacPlus, and WMA; SBR (spectral-band replicaparametric stereo; QSound MIDI; 3-D audio; and G723-1 and G729AB VOIP (voice-over-Internet Protocol) codecs. The midrange Diamond 212GP RISC controller offers DSP support, including 16 MACs (multiply/accumulates), 16 multipliers, minimum/maximum operations, clamps, sign extend, and NSA instructions. It includes instruction and data caches, as well as user-selectable local-memory sizes, and it competes with ARM9-based approaches for better processing performance and lower power consumption. It uses a 0.58-mm<sup>2</sup> cell area in a 0.13-micron process and consumes 0.085 mW/MHz with the 0.13LV libraries or 0.135 mW/MHz with the 0.13G libraries.

The midrange Diamond 232L RISC-processor core includes a full MMU (memory-management unit) to support the requirements of the Linux operating system. It includes the same DSP support as the 212GP. The core requires a 0.71-mm² cell area in a 0.13-micron process and consumes 0.10 mW/MHz with the 0.13LV libraries or 0.145 mW/MHz with the 0.13G libraries

The high-performance, threeissue Diamond 570T static superscalar processor core com-

petes with the ARM1136JF-S core based on EEMBC (EDN Embedded Microprocessor Benchmark Consortium) benchmarks. The core includes both a 32-bit input and a 32bit output queue that support direct access to data from the pipeline with no loads or stores. The core uses a 0.96-mm<sup>2</sup> cell area in a 0.13-micron process and consumes 0.11 mW/MHz with the 0.13LV libraries or 0.15 mW/MHz with the 0.13G libraries. The highest performance Diamond 545CK licensable core delivers digital-signal processing using a three-issue VLIW (very-long-instructionword) processor containing eight MACs that support SIMD (single-instruction-multipledata) operations. The core includes a Viterbi accelerator to support communications baseband applications.

The price for the Diamond 108Mini is \$75,000 for a single-use license with a royalty fee of 5 cents per core. Tensilica's XCC optimizing compiler and Eclipse-based Xplorer IDE support software development on these processors with a clock-cycle-accurate, pipeline-modeled instruction-set simulator; a Gnu-based tool chain, including an assembler, a debugger, a profiler, and a linker; and optimized C libraries. Operating-system support for these cores includes Accelerated Technology's (www. acceleratedtechnology.com) Nucleus Plus, micro-Itron from Sophia Systems (www.sophia. com), Tensilica's runtime XT-OS, and open-source eCOS. Linux support for the Diamond Standard 232L is available MontaVista's (www. from mvista.com) Linux Professional.

−by Robert Cravotta

►Tensilica, www.tensilica.

com.

#### FROM THE VAULT

By 2006, homes worldwide will be plugged into an international broadband network

... Dozens of technically feasible and marketable broadband functions will come into common use over the next 25 years, including video shopping, alarm and metering systems, video libraries, electronic-mail systems, office work and EDP time-sharing access. To support such activity, we will need 100-Mbps capacity in 100 million homes by 2006.

Jeff Montgomery, president, Gnostic Concepts, *EDN*, Oct 14, 1981

#### **DILBERT** By Scott Adams

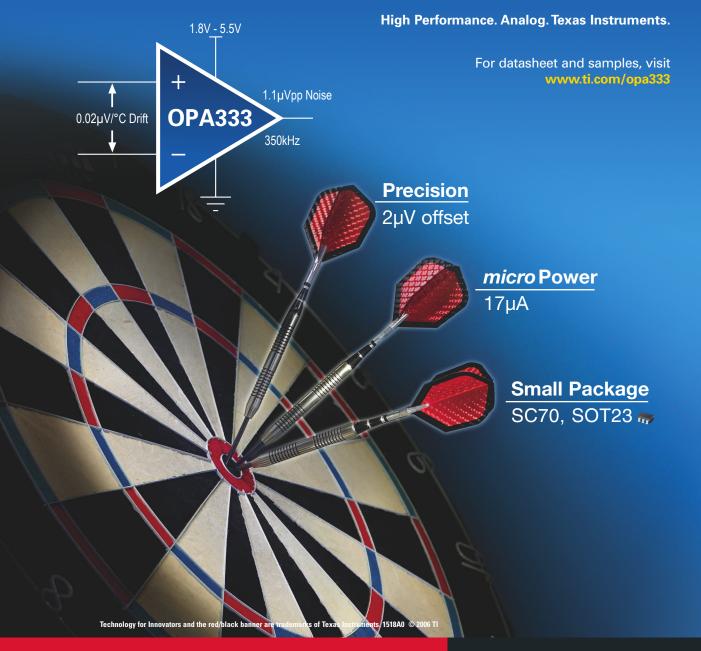

## Right on Target

### Zerø-Drift Operational Amplifier

The new OPA333 zero-drift operational amplifier combines excellent precision, micropower and tiny packaging to achieve breakthrough performance. Featuring operation down to 1.8V, the OPA333 targets demanding applications in medical instrumentation, temperature measurement, test equipment and consumer systems.

## Sigma-C and Mentor make strides in DFM

nnouncements from Sigma-C and Mentor Graphics bode well for IC-design groups wanting to spot and fix lithography hot spots in their IC layouts before they send their designs to the mask shop. Sigma-C has announced the Solid+ microlithography simulator for design and OPC (optical-proximity correction).

Meanwhile, Mentor Graphics' Calibre group has introduced a tool for mask makers. However, the company says that the product's underlying pixelbased simulation engine sets the stage for a bigger release, this year, of a design-centric microlithography simulator. The microlithography-simulation niche of the DFM (designfor-manufacturing) market is becoming important as process geometries shrink below 90 nm, driving mask costs into the millions of dollars. Masks on these processes require OPC on all layers and thus

take more effort and cost.

With Solid+, engineers use full-chip, third-party lithography simulators to locate trouble spots and then use Solid+ to do detailed 3-D analysis, says Peter Feist, chief executive officer of Sigma-C. Users feed Solid+ a GDSII file, and, after simulation, the tool generates a resist profile. Engineers can then overlay their desired layout and the simulated print showing how it would appear in the photo resist, thus exposing areas in which violations are likely to occur. The company has thus far identified three usage models for the tool.

First, IC and custom-cell de-

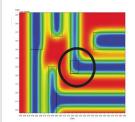

Sigma-C's Solid+ locates trouble spots (left) and then performs detailed 3-D analysis (right).

signers can use the tool to perform resist-level simulation of layout and cells larger than 20×20 microns to let designers know whether the photo resist can accurately produce their patterns at smaller process nodes. Second, engineers can use the tool for developing OPC rules decks. Mask problems often occur because OPC rules are not well-defined; vendors build them using results from less-accurate 2-D simulators. Designers can use Solid + to ensure the accuracy of OPC rules decks.

Mentor Graphics' OPC verification tool, OPCverify, mainly targets mask makers and qualifiers who want to check pattern fidelity before committing to a mask. The tool takes in the drawn layer, an OPC-

corrected layer, and a run file and then uses a new pixelbased engine to simulate a silicon image as it would show up on the output of a scanner. The tool then gives a contour of every shape on the chip.

OPC engineers can also use the tool to ensure OPC rules are robust on many designs. OPCverify sets the stage for an upcoming release targeting IC designers. Lithographic simulation will become commonplace, but, to make it effective, designs have to take OPC into account-essentially imitating everything a fab facility does. "As we get to 65 and 45 nm, pattern fidelity is a huge issue," says Charlie Albertalli, product manager for Mentor. "It is getting harder and harder with lowk processes to absolutely replicate a design shape. Certain topologies look good at nominal dosage and focus, but, as soon as you remove the OPC, the image rapidly falls apart."

—by Michael Santarini ▶Sigma-C, www.sigma-c.

COIII.

**►Mentor Graphics**, www. mentor.com.

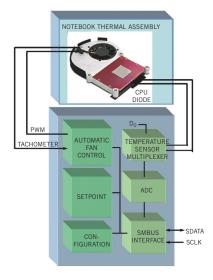

## Thermal escalation drives need for controlled active cooling

Thermal issues continue to escalate in the PC-processor sector. Early processors required huge passive heat sinks and then fans dedicated to the processor-cooling task. Now, reliable systems need active monitoring of systems and even chip temperature with real-time fan control. Andigilog targets just such applications with its ThermalEdge technology. The company has just announced two thermal-management chips: the aSC7512, which targets traditional motherboard designs, and the aMC8500 for the new BTX (Balance Technology Extended) technology. Intel (www.intel.com) designed BTX for shrinking form factors, and it moves the PC to mechanically separate subsystems with different cooling, power, and other needs.

The aSC7512 includes an on-chip temperature sensor and remote die-temperature sensing capability using a connection to the diode integrated on a processor die. The chip supports three- and four-wire fans and integrates a digital filter that makes for smoother fan operation. The aMC8500 can drive a 1A, brushless-dc fan and integrates the requisite MOSFET motor drives. Andigilog will ship samples of the chips, as well as reference designs, in April. The aSC7512 will sell for \$1.50 (1000), and the aMC8500 will sell for \$1.45 (1000).—by Maury Wright

>Andigilog, www.andigilog.com.

Connecting to an on-chip diode, the aSC7512 thermal-management chip takes real-time die-temperature readings and offers dynamic cooling-fan control.

PROCESSORS | SOFTWARE | TOOLS | SUPPORT

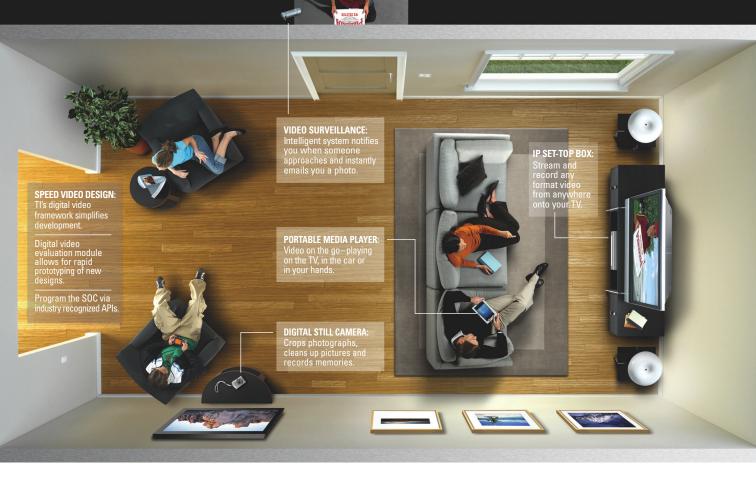

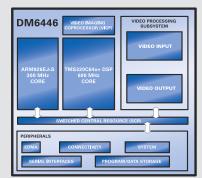

Now that DaVinci products are here, your digital video innovations are everywhere.

That's the DaVinci Effect.

Davinci™ Technology makes astounding creativity possible in digital video devices for the hand, home and car. The DaVinci platform includes digital signal processor (DSP) based SoCs, multimedia codecs, application programming interfaces, application frameworks and development tools, all of which are optimized to enable innovation for digital video systems. DaVinci products will save 0EMs months of development time and will lower overall system costs to inspire digital video innovation. So what are you waiting for? You bring the possibilities. DaVinci will help make them real.

IP Set Top Box

#### What is DaVinci?

#### **Processors: Digital Video SoCs:**

- TMS320DM6446 Video encode/decode

- TMS320DM6443 Video decode

#### **Performance Benchmarks:**

| STANDALONE CODECS           | DM6446                           | DM6443 |

|-----------------------------|----------------------------------|--------|

| MPEG-2 MP ML Decode         | 1080i+ (60 fields<br>/30 frames) | 720p+  |

| MPEG-2 MP ML Encode         | D1+                              | n/a    |

| MPEG-4 SP Decode            | 720p+                            | 720p+  |

| MPEG-4 SP Encode            | 720p+                            | n/a    |

| VC1/WMV 9 Decode            | 720p+                            | 720p+  |

| VC1/WMV 9 Encode            | D1+                              | n/a    |

| H.264 (Baseline) Decode     | D1+                              | D1+    |

| H.264 (Baseline) Encode     | D1+                              | n/a    |

| H.264 (Main Profile) Decode | D1+                              | D1+    |

#### Tools: Validated Software and Hardware Development

- DVEVM (Digital Video

- Evaluation Module)

### velopment

#### MontaVista Development Tools Code Composer Studio IDE

#### Software: Open, Optimized and Production Tested

- Platform Support Package

- MontaVista Linux Support Package

- Industry-recognized APIs

- Multimedia frameworks

- Platform-optimized, multimedia codecs:

- H.264 | AAC | G.729ab - MPEG4 | - WMA9 | - WMV9/ - H.263 | - MP3 | VC1

- H.263 MP3 - MPEG2 - G.711

- JPEG G.728 - AAC+ - G.723.1

- >>> For complete technical documentation or to get started with our Digital Video Evaluation Module, please visit

www.thedavincieffect.com

Automotive Infotainment Di

Digital Still Camera

Digital Video Innovations

Video Surveillance

Video Phone & Conferencing

DaVinci, Code Composer Studio IDE, Technology for Innovators and the red/black banner are trademarks of Texas Instruments. 1321A0 © 2006 TI

#### **VOICES**

#### Round table mulls hard-IP-at-board-level concept

ometimes, a panel discussion ends up more like a round table. That scenario happened at DesignCon in February, with a panel that design consultant Pallab Chatterjee organized on hard IP (intellectual property) and whether it can exist for board-level designs. At the chip level, "hard IP" refers to a block of circuitry that a designer has verified, placed, and routed, so that you can drop it into a chip design intact during the physical-design process. In some cases, you can insert hard IP into the design at the foundry just before mask creation.

Can a similar concept exist for board-level design? Chatterjee opened the discussion, observing that some board-level reference designs go all the way to specifying components and providing Gerber files for creating board film. But then he pointed to several examples of designs in which the form factor of the final product makes it impossible to use the reference design without significant modification, and this modification invalidates the electrical verification designers perform on the reference design.

The panelists included Chatterjee; Vipul Badoni, senior manager of the high-speed-I/O-Applications-engineering group at Altera; Jerry Durand, chief executive officer of Durand Interstellar; and John Isaac, director of market development for the systemsdesign division at Mentor Graphics.

#### What comes with an Altera reference board?

Badoni: "If you purchase one of our reference designs, you get a full [Cadence] Allegro database with constraints, schematics, and documentation with design guidelines. We even give

you the guidelines we gave to the pc-board designer to design our board.

Isaac: One of the most important things chip vendors deliver to customers are models. Any customer today that takes a reference design as a drop-in core, slaps it in their

design, adds a little logic, and intends to make 100 of them is crazy. The performance of signal-integrity models that vendors supply is important.

How much information do you have to model that is in the reference design that may not be just datasheet specs of the FPGA? Do you provide signal-integrity models for the traces that connect the reference design to the outside world?

Badoni: Yes. We work with vendors to get connection models in with our reference designs. In modeling, if you get garbage in, you get garbage out, so you have to be careful with what you supply. Don't substitute a Micron DIMM for an Infineon DIMM and expect it to work. You have to secure the right models to make sure they work.

#### What are the worst problems designers face today?

Badoni: The most prevalent problem we are dealing with today is pow-

Durand: It's a problem because of built-in contradictions. For instance, the powerdelivery specs on complex chips often say the parts are supposed to have low impedance to the power and ground planes. But if that chip is in a MicroBGA package, you are using 6-mil laser-drilled vias that go down only 0.005 in., or one layer. So, it gets hard to have super low impedance to power and ground planes that are 0.020 in. below the via.

Badoni: Monitoring the power-delivery systems is also tough because you have to model passives in Spice, which

Any customer todav that takes a reference design as a drop-in core, slaps it in their design, adds a little logic, and intends to make 100 of them is crazy.

is not inherently a passivemodeling technology. You have to figure out what capacitors you can put in your system.

Durand: Power is a big problem, especially in MicroBGA packages in which a single device can have a mix of pins with different voltages. Layout is difficult with alternating 2.5, 1.8, and 3.3V pins. You can't even run a heavy bus up to catch those pins. If you had four in a row, you could drill a via to connect them, but if you intersperse them, you wind up with fine traces running your power into the lead; it is the only physical way to do it.

#### Who owns SIP (system-inpackage) design: IC designers, pc-board designers, or a separate group?

Chatterjee: Speaking from the chip-design world, I don't know anyone who would willingly want to take on that set of problems.

Isaac: One of the advantages of SIPs is that a lot of the parts are off-the-shelf. You may design an IC to put in a SIP and then grab parts from other people and add some discretes. It soon becomes a cross between IC and pcboard design.

> -by Ron Wilson and Michael Santarini

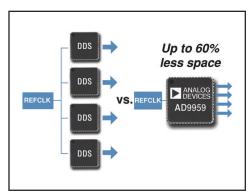

## Precise synchronization—for precise control. In synthesizer designs, analog is everywhere.

#### **Single-Chip Multichannel DDS Solution**

#### AD9959/AD9958: 32-bit DDS precision ...

- 4/2 synchronized DDS channels @ 500 MSPS

- 4/2 integrated 10-bit DACs

- >53 dBc wideband SFDR

- 32-bit frequency tuning resolution

- 14-bit phase offset resolution

- 10-bit output amplitude scaling resolution

- · Available in a 56-lead LFCSP package

- Pricing: AD9959 (quad-DDS): \$37.14/1k \$U.S. AD9958 (dual-DDS): \$20.14/1k \$U.S.

#### ... where it matters

- · Phased array radar/sonar

- · Agile local oscillator

- Instrumentation

- · Synchronized clocking

- · RF source for AOTF

Old multichip solution vs. new quad DDS.

## New multichannel synthesizers reduce parts and design complexity

Designing synthesizers with multiple channels has never been easier. That's because ADI offers the industry's first multichannel DDS ICs. With inherent output synchronization, these unique single-chip solutions significantly decrease design time and overall system complexity. What's more, the new AD9958 and AD9959:

- Achieve 0.022° phase tuning resolution for precise synchronization

- Feature excellent channel-to-channel isolation

- Eliminate multiple parts and external circuitry—reducing PCB space up to 60%

- Lower system costs as much as 15% vs. multicomponent designs

- Consume <165 mW per channel

Experience greater signal control through precise synchronization functionality—with ADI's multichannel DDS devices. And for compatible clocks and comparators, visit our website.

#### **AGLOBAL DESIGNER**

#### Korea gets WiMax certification lab

omentum for WiMax (Worldwide operability for Microwave Access) wireless-broadband technology continues to build-especially outside North America. Korea is an early adopter of wireless services and is leading the WiMax charge with a new certification lab. To handle the expected deluge of WiMax gear, the WiMax Forum chose Spain's Cetecom Laboratories (www.cetecom.es) as the first laboratory and recently added Seoul, South Korea's TTA (Telecommunications Technology Association www.tta.or.kr) as the second.

TTA will likely specialize in certification of products that conform to the coming mobile flavor of WiMax, IEEE 802.16e. South Korea is launching WiBro (wireless-broadband) technology that is essentially

the basis for mobile WiMax. TTA plans to have the WiMax lab operating by the second quarter of this year. It expects to certify the first commercial mobile-WiMax product in the first quarter of 2007.

In other WiMax developments, Cetecom Laboratories is also preparing to offer mobile-WiMax certification. The lab is jointly developing a protocolconformance tester with Aeroflex (www.aeroflex.com). Cetecom and UK-based picoChip (www.picochip.com) have just announced that the tester would rely on the PC102 DSParray chips and the PC8530 software stack from picoChip. Cetecom hopes to begin mobile-WiMax testing by the end of the year.

-by Maury Wright **▶WiMax Forum**, www.wimax forum.org.

#### **SOC HOUSE** PARTNERS WITH MALAYSIAN FAB

Belgium company Essensium, a provider of SOC (systemon-chip)- and ASIC-design services, recently received a significant boost with a funding infusion from investment company Atlantic Quantum, which Khazanah National (www.khazanah.com.my) owns. Khazanah also owns foundry Silterra (www.silterra. com). The €6 million investment will allow Essensium, a spin-off of IMEC (www.imec. be), to become an independent company, although it has access to IMEC's wireless, SOC, and system-in-package intellectual property.

-by Maury Wright

**⊳Essensium**, www. essensium.com.

#### SOM concept adds versatility to embedded computing

According to Advantech, SOM (system-on-module) computing is set to grow rapidly this year as more companies adopt the concept. The company sees SOM as a good fit for applications that have product volumes of 1000 to 10,000 units. At less than that level, a conventional single-boardcomputing approach is the preferred option; at high volumes, a custom design becomes more economic.

In the 1000- to 10,000-unit range, Advantech designs a

#### Oscillator pushes to 192 GHz for detection applications

Taiwan-based UMC claims to have produced the highest frequency VCO (voltage-controlled oscillator) yet to be fabricated in silicon. The University of Florida's Department of Electrical and Computer Engineering (Gainesville, FL, www.ece.ufl.edu) designed the VCO, which operates at 192 GHz. UMC officials believe that designers can use the VCO in a variety of sensitive detection applications, such as chemical detection, detection through fabric, imaging through fog and clouds, and even the detection of skin cancer.

UMC built the VCO using its 130-nm RF-CMOS process. The device has a "push-push" design, meaning that the output frequency is only double the core frequency, whereas some VCOs multiply the core frequency by three or four, resulting in relatively weak output. UMC's VCO provides -20 dBm and consumes 11 mA from a 1.5V supply.-by Maury Wright

UMC, www.umc.com.

target board for the application. The board contains the functions that the task requires in addition to the basic computing capability. It then provides the computing power in the SOM, which plugs into the system board. This approach provides advanced computing power in an easyto-use format, because the critical parts of the designthose close to the CPU itselfexist in a fully developed, stable condition. Users also have the option of changing or upgrading processors by replacing the module.

Advantech's SOM-device support includes Com Express, ETX, PCI-bus SOM-144, and the company's A200 series of modules. Advantech based the A2200 RISC platforms on PXA and other ARM9 chips for mobile and low-power applications. Advantech states that, although recent coverage associates the SOM concept with newer, high-power processors, it can host any level of CPU from 486 to Pentium M or Xeon chips. The company aims to provide a complete design package, interpreting the "platform" as hardware, software, and any required design services. Distributed design centers can access Advantech's corporate IP (intellectual-property) resources, and the company's in-house prototyping production line can produce sample lots of as many as 30 pieces of a board design, with a target time of two months from design start to delivery.

Advantech is working on a modular-I/O concept to match the processor boards with preconfigured modules for applications that require connectivity exceeding that of the standard modules.

> -by Graham Prophet, EDN Europe

Advantech, www. advantech.com.

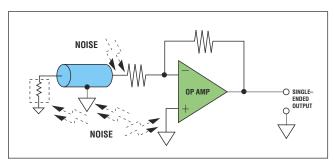

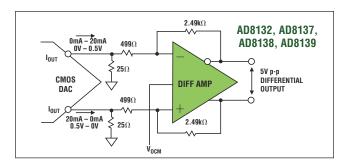

### A series of engineering insights by Analog Devices.

### The Importance of Differential Measurement

Many real world applications require amplifying a very small signal in a high noise environment. Usually, the signal sensor is located some distance from the amplifier. As a consequence, a large amount of noise and hum is often introduced.

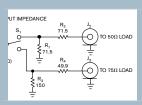

Effective signal recovery often depends on carefully choosing the optimum amplifier for a particular application. There are three common types of systems in use: single-ended input and output (operational amplifier based), differential input, single-ended output (instrumentation amplifier based), and differential input and differential output (differential amplifier based) systems. Some designers may be tempted to use a single-ended, shielded cable system, similar to that shown in Figure A.

Figure A. A single-ended measurement system

Here, the input is applied between the shielded cable and common or "ground," then travels through the cable to the op amp. A single-ended system like this is very prone to noise pickup because the signal is referenced to ground, i.e., the signal flows through the system ground, with noise being added along the way. With a single-ended system like this, both the signal and the noise are amplified. The common practice of removing the noise at the amplifier output, using low-pass, high-pass, or band-pass filtering, is often ineffective. In some cases, the total noise can be much greater than the signal itself.

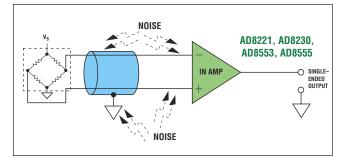

Figure B. A differential input, single-ended output measurement system

Figure B shows a better method for recovering weak signals. Here, the input signal source is differential. Simply stated, this means that the signal is applied *between* two input lines, with *no* signal traveling through the ground connection. This type of system normally uses an in-amp which has a differential input and a single-ended output. Much of the noise that is the same (common mode) on both lines is rejected by the in-amp, which only amplifies the differential input signal.

Note that the inputs of most instrumentation amplifiers require a dc return path (using resistors, for example) for the amplifier's input bias currents. This is very important for ac-coupled, single-supply applications where it is also often necessary to have the amplifier's input common-mode reference and output reference raised above ground.

Figure C. A differential input, differential output amplifier used as a high-speed DAC buffer

Figure C is a system featuring an amplifier that has both a differential input and output. These are commonly used in high bandwidth applications, such as driving ADCs or buffering DACs.

For more information on using operational amplifiers, instrumentation amplifiers, differential amplifiers, and other signal processing components, please visit <a href="https://www.analog.com">www.analog.com</a>.

In addition, you can view these following online seminars: "Looking at the World Different(ial)ly" and "In-Amps: Common Applications Problems and Solutions" both at: www.analog.com/onlineseminars.

Finally, you can download or receive a hard copy of the design handbook "A Designer's Guide to Instrumentation Amplifiers, 2nd Edition" at <a href="https://www.analog.com/inampguide">www.analog.com/inampguide</a>.

Author Profile: **Chuck Kitchin** has been a hardware applications engineer with Analog Devices for 29 years. In addition to developing new circuits, he has published three books and close to 100 technical articles.

#### **Multi-Frequency, Low Jitter Oscillators**

The Si530 and Si550 families of XOs and VCXOs are a new class of oscillators that support multi-frequency operation between 10 MHz and 1.4 GHz while delivering ultra-low jitter (<0.5 ps RMS typical OC-192). With patented DSPLL® technology, Silicon Labs is able to move frequency control and tuning from a complex resonator to a single CMOS IC. These devices eliminate long, unpredictable lead times typically associated with high-frequency, low-jitter oscillators and offer total frequency stability over time and temperature that is more than five times better than competing SAW devices.

| Part Number    | Туре          | Stability<br>(ppm) | Frequency Range | Output<br>Formats     | Package<br>Size | Supply<br>Voltage |

|----------------|---------------|--------------------|-----------------|-----------------------|-----------------|-------------------|

| Si530<br>Si530 | XO<br>Dual XO | ±20<br>±50         | 10 MHz–1.4 GHz  | LVPECL<br>LVDS<br>CML | 5x7mm           | 3.3 V<br>2.5 V    |

| Si534          | Quad XO       | ±50                |                 | CMOS                  |                 | 1.8 V             |

| Si550          | VCXO          | ±20<br>±50<br>±100 | ±20             | LVPECL                |                 | 3.3 V             |

| Si552          | Dual VCXO     |                    | 10 MHz–1.4 GHz  | LVDS<br>CML           | 5x7mm           | 2.5 V             |

| Si554          | Quad VCXO     |                    | 100             | CMOS                  |                 | 1.8 V             |

#### **Actual Size**

5 mm

**Unmatched Performance**

**Highest Reliability**

**Shortest Lead Times**

**Standard Pinouts**

Product details: www.silabs.com/VCXO

SILICON LABORATORIES www.silabs.com

## Support Across The Board.

Starting with in-depth design support all the way through to total supply chain management – Avnet Electronics Marketing is there for you.

From concept to reality, we deliver:

Consultative engineering support and services

Focused product specialization

The broadest supplier partnerships in the industry

Over \$1 billion in top moving inventory "on the shelf"

World-class supply chain services

But, partnering with Avnet Electronics

Marketing means much more than just

having access to the industry's broadest

array of design and supply chain services.

It means working with a company that is truly

focused on exceeding your needs and

expectations – a company that is dedicated

to giving you Support Across The Board."

Ready.

Set.

Go to market.™

Enabling success from the center of technology ™

1 800 332 8638 www.em.avnet.com

#### BY BONNIE BAKER

#### Choosing SAR versus highspeed delta-sigma ADCs

elta-sigma-ADC technology has caught up to that of SAR (successive-approximation-register) ADCs in sampling frequency. A crossover in the sampling-time regions of approximately 100 kHz to 1 MHz exists in both types of devices. These two types of converters also match in most key specifications. For instance, are you concerned about

the dc characteristics of offset voltage and gain error, or are you more concerned about the ac specifications, such as noise or THD (total har-

monic distortion)? You may find SAR and high-speed delta-sigma converters that have equivalent specifications in the dc realm, as well as the ac specifications.

So which device do you choose for your application circuit? To make that determination, you need to compare the operation of these two devices. A/D-conversion latency is the time the

SIRAL NOISE

SINGLE SAMPLE

GIVES NOISIER

RESULTS

MULTIPLE SAMPLES,

AVERAGED

SAMPLING SAR ADC

OVERSAMPLING DELTA-SIGMA ADC

Figure 1 A SAR converter takes several "snapshots," capturing the waveform. The delta-sigma ADC averages during the sample period, providing signal filtering.

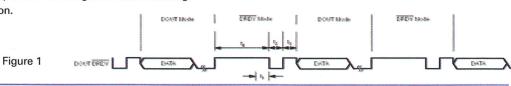

ADC takes to go from one sample to the next, including the data-retrieval time. SAR-converter latency comprises a "snapshot" of the signal and the serial retrieval of the data. In contrast, the delta-sigma ADC has a larger output-code delay because the converted signal does not correspond to a single point in time. The delta-sigma converter quickly averages the input for a predetermined time before outputting the digital code at higher speeds (Fig**ure 1**). The trade-off between the converters is that the delta-sigma ADC consumes more power due to higher clock rates.

A common disappointment when you use a SAR converter is the presence of large variance in the output code for a dc input signal. The problem often is not the converter, but how you implement the application circuit. A SAR converter has a wide input bandwidth and fast reaction to signal changes. The one-time-sample-per-conversion architecture effectively captures the signal and its noise. This type of converter in a noisy environment requires a highorder, antialiasing filter. The addition of an antialiasing filter solves the noise problem but increases the settling time of the converter system. The system settling time is an issue in multiplexed-system applications.

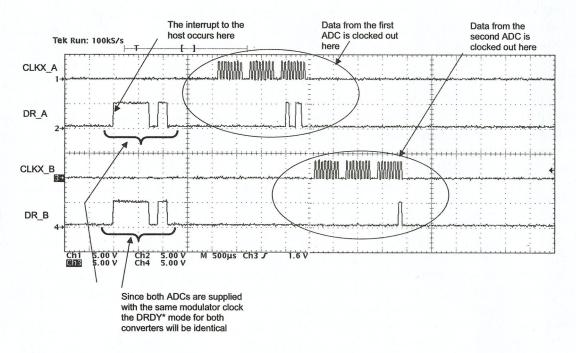

In contrast, a delta-sigma converter averages multiple samples at a higher data rate for each conversion result. The digital filter in these converters acts as an antialiasing filter, so that the converters need only an external second-order lowpass filter on the analog input. A delta-sigma converter easily handles signal noise with its internal digital-filtering system. However, if you present a step input to the delta-sigma-converter input, the converter also requires time to settle. The on-chip digital filter requires time to refill and resettle.